# **CHAPTER 2**

#### **Logic Gates**

#### Contents

- Boolean Variables & Truth Tables

- OR Operation

- AND Operation

- NOT Operation

- NOR Operation

- NAND Operation

- The Exclusive- OR Gate

- The Exclusive-NOR Gate

- INTEGRATED CIRCUIT LOGIC FAMILIES

#### **Boolean Variables & Truth Tables**

| LOGIC 0     | LOGIC 1      |

|-------------|--------------|

| False       | True         |

| Off         | On           |

| Low         | High         |

| No          | Yes          |

| Open Switch | Close Switch |

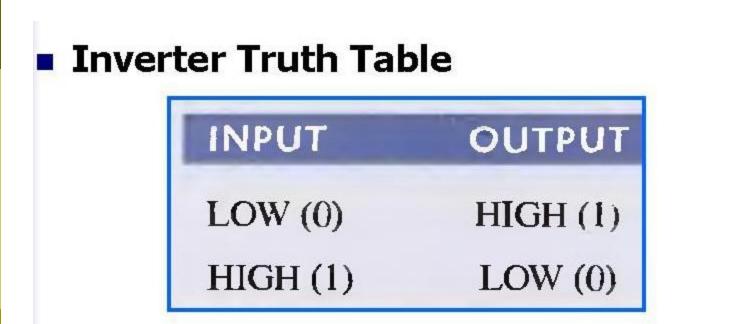

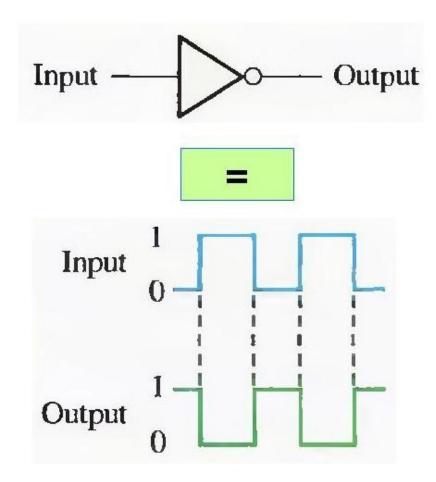

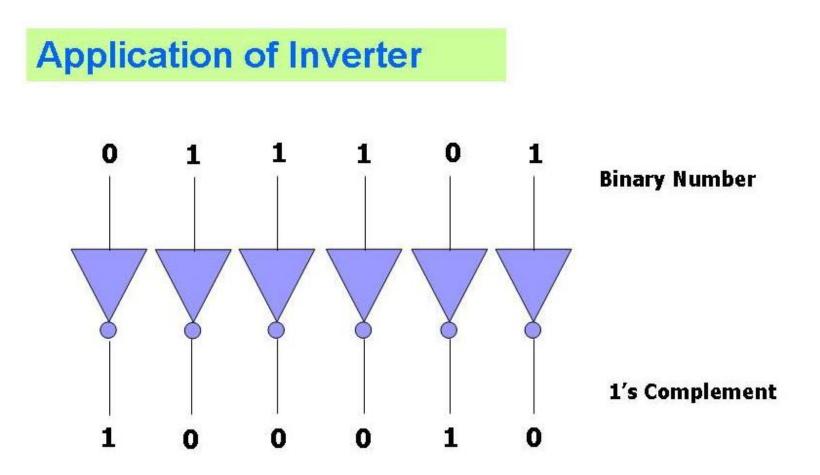

#### Inverter

- The inverter (NOT circuit) performs the operation called inversion or complementation.

- The inverter changes one logic level to the opposite level.

- In terms of bits, it changes a 1 to a 0 and a 0 to a 1.

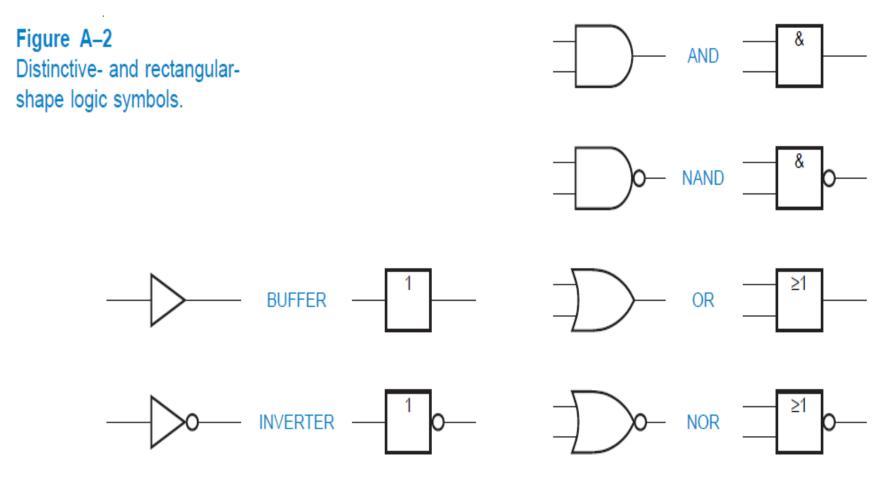

- Standard logic symbols for the inverter is,

-

Distinctive shape symbols with negation indicators

- A table such as this is called a truth table.

- When a HIGH level is applied to an inverter input, a LOW level will appear on its output.

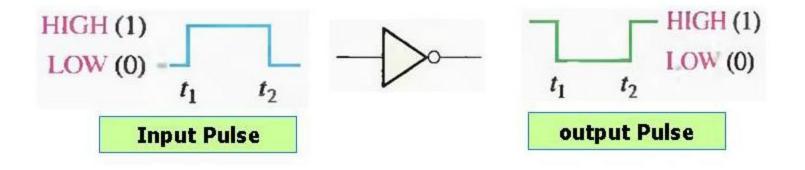

#### Inverter

- When the input is LOW, the output is HIGH and vice versa.

- producing an inverted output pulse.

- Standard logic symbols for the inverter is,

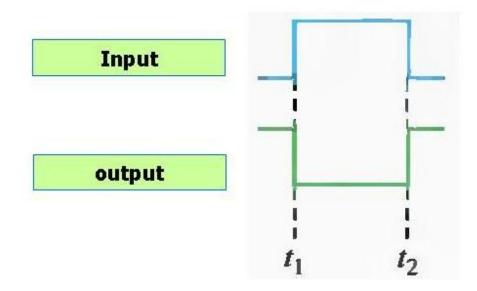

#### **Timing Diagram of Inverter**

timing diagram is basically a graph that accurately displays the relationship of two or more waveforms with respect to each other on a time basis.

# Timing Diagram Example

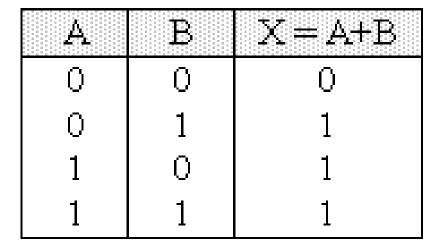

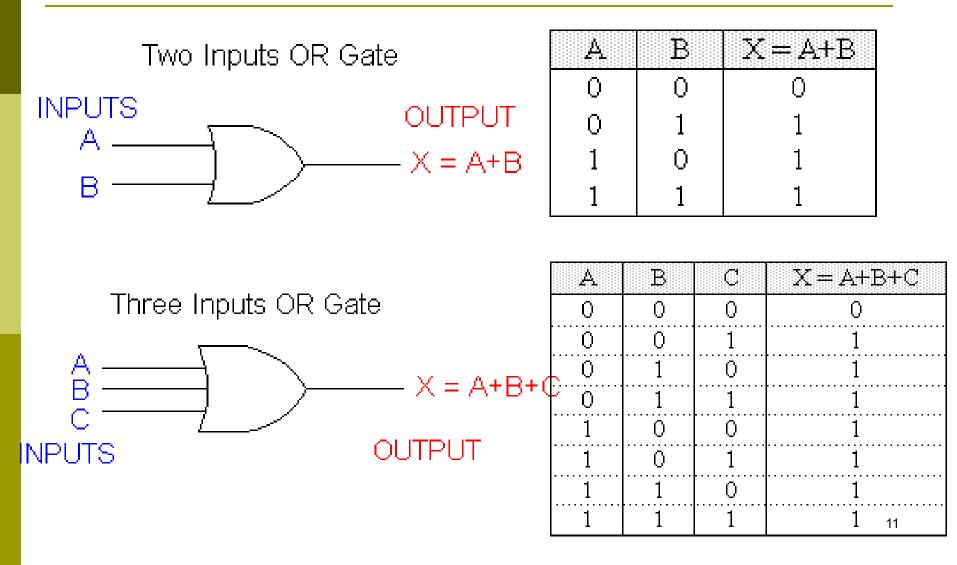

## **OR** Gate

- An OR gate can have two or more inputs and performs what is known as logical addition.

- Standard logic symbols for the OR gate showing two input and single output.

$$B = \sum_{X \in X} X$$

- An OR gate can have any number of inputs greater than one.

- An OR gate produces a HIGH on the output when any of the inputs is HIGH.

- The output is LOW only when all of the inputs are LOW.

# Logic Expression of OR

The operation of a 2-input OR gate can be expressed as follows: If one input variable is A, if the other input variable is B, and if the output variable is X, then the Boolean expression is

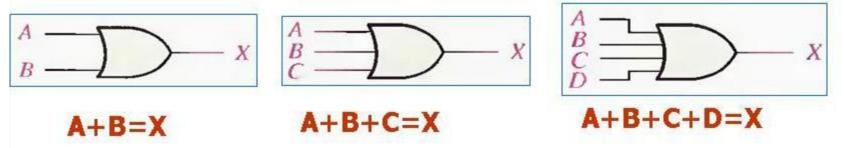

Boolean expressions for OR gates with two, three, and four inputs,

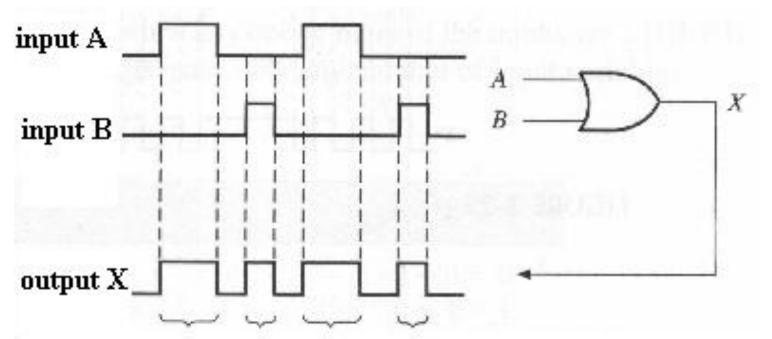

# Timing Diagrams of OR gates

When either input or both inputs are HIGH, the output is HIGH

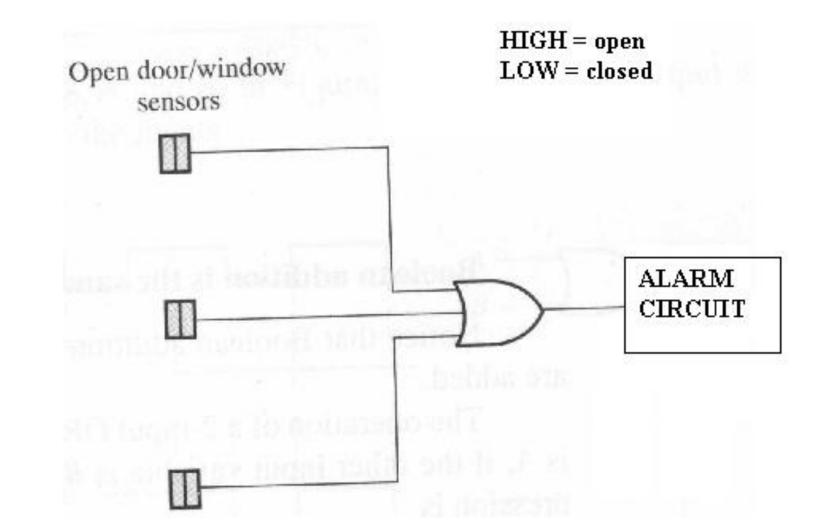

# An application: Alarm System

## AND Gate

#### **AND Gate**

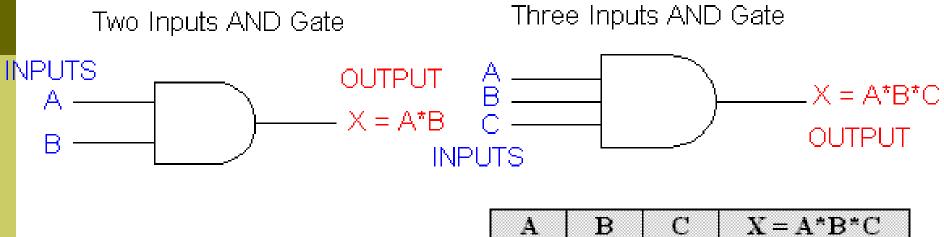

- The AND gate is one of the basic gates that can be combined to form any logic function.

- An AND gate can have two or more inputs and performs what is known as logical multiplication.

- The term gate is used to describe a circuit that performs a basic logic operation.

- The AND gate is composed of two or more inputs and a single output.

- Standard logical symbol of AND gate is,

## AND Gate

#### Operations of an AND Gate

- An AND gate produces a HIGH output only when all of the inputs are HIGH.

- When any of the inputs is LOW, the output is LOW.

- Therefore, the basic purpose of an AND gate is to determine when certain conditions are simultaneously true.

## **AND** Operation

| Α | B | $X = A^*B$ |

|---|---|------------|

| 0 | 0 | 0          |

| 0 | 1 | 0          |

| 1 | 0 | 0          |

| 1 | 1 | 1          |

| A | В | С | $X = A^*B^*C$ |

|---|---|---|---------------|

| 0 | 0 | 0 | 0             |

| 0 | 0 | 1 | 0             |

| 0 | 1 | 0 | 0             |

| 0 | 1 | 1 | 0             |

| 1 | 0 | 0 | 0             |

| 1 | 0 | 1 | 0             |

| 1 | 1 | 0 | 0             |

| 1 | 1 | 1 | 1 17          |

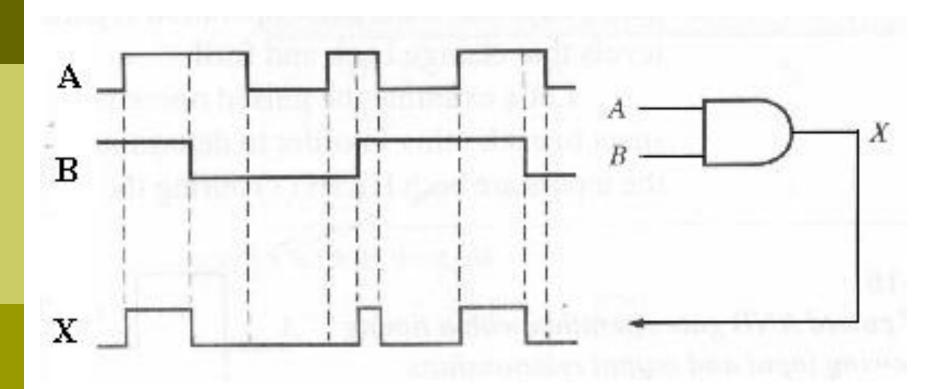

# Timing Diagrams of AND gates

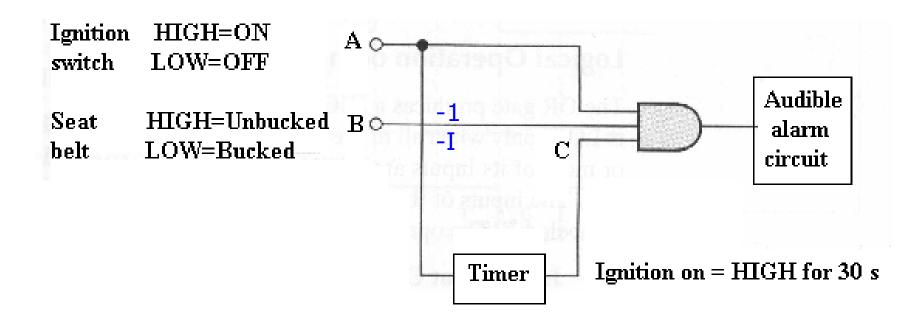

## An application: A Seat Belt Alarm System

### **NOR Operation**

Two Inputs NOR Gate

| INP | UTS | OR        | NOR      |

|-----|-----|-----------|----------|

| A   | B   | X = A + B | X= (A+B) |

| 0   | 0   | 0         | 1        |

| 0   | 1   | 1         | 0        |

| 1   | 0   | 1         | 0        |

| 1   | 1   | 1         | 0        |

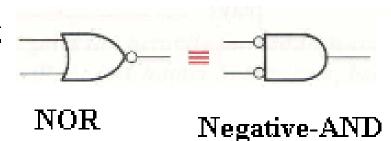

# Negative AND equivalent of a NOR gate

Standard symbols representing the two equivalent operations of the NOR gate.

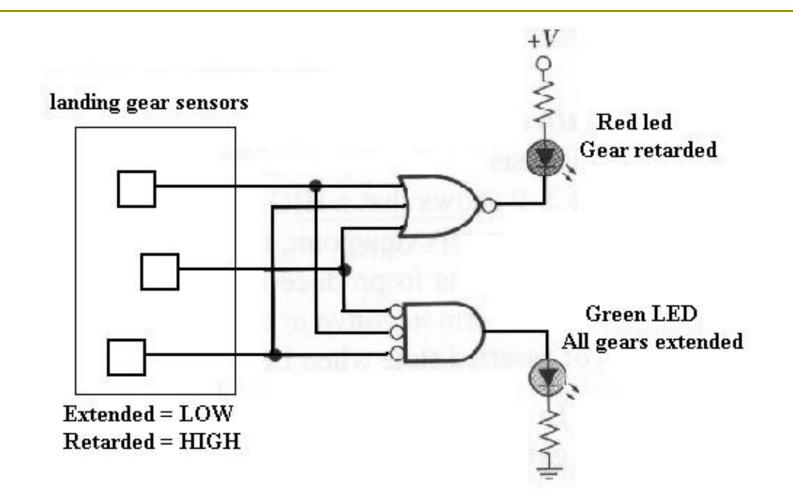

# An application: An aircraft landing indicator

## NAND Gate

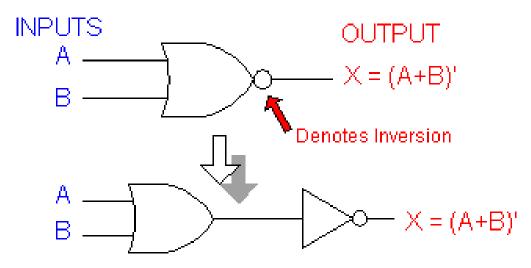

- The NAND gate is a popular logic element because it can be used as a universal gate. NAND gates can be used in combination to perform the AND, OR, and inverter operations.

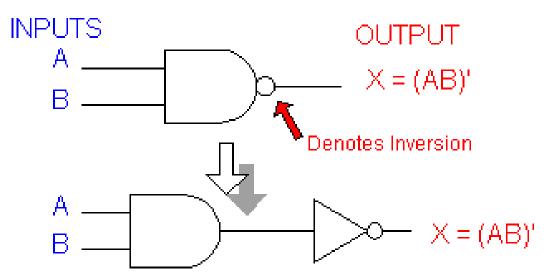

- The term NAND is a contraction of NOT-AND and implies an AND function with a Complemented (inverted) output.

- The standard logic symbol for a 2-input

- NAND gate and its equivalency to an AND gate followed by an inverter.

## **NAND** Operation

Two Inputs NAND Gate

| INP | UTS AND |        | NAND    |

|-----|---------|--------|---------|

| A   | В       | X = AB | X= (AB) |

| 0   | 0       | 0      | 1       |

| 0   | 1       | 0      | 1       |

| 1   | 0       | 0      | 1       |

| 1   | 1       | 1      | 0       |

## Logic Expression for NAND Gate

The Boolean expression for the output of a 2input NAND gate is,

$$X = \overline{AB}$$

two input variables A and B, are first ANDed and then complemented, as indicated by the bar over the AND expression.

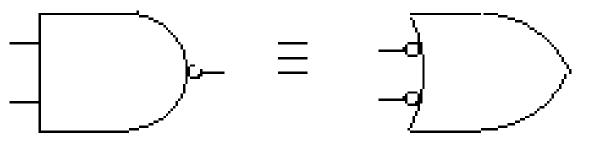

# Negative OR Equivalent Operation of the NAND Gate

NAND

Negative-OR

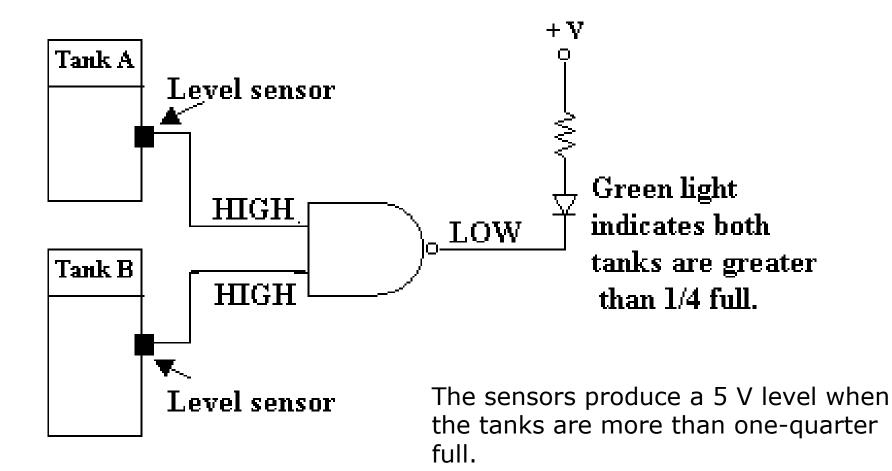

#### An application: A Manufacturing Plant Tank Indicator

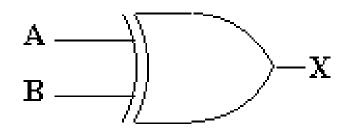

#### The Exclusive- OR Gate

| Inputs |   | output |  |  |

|--------|---|--------|--|--|

| A B    |   | Х      |  |  |

| 0 0    |   | 0      |  |  |

| 0 1    |   | 1      |  |  |

| 1      | 0 | 1      |  |  |

| 1 1    |   | 0      |  |  |

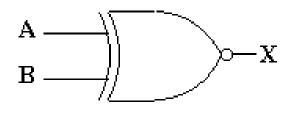

#### The Exclusive-NOR Gate

| Inputs |   | output |  |  |  |  |

|--------|---|--------|--|--|--|--|

| A B    |   | Х      |  |  |  |  |

| 0      | 0 | 1      |  |  |  |  |

| 0      | 1 | 0      |  |  |  |  |

| 1      | 0 | 0      |  |  |  |  |

| 1      | 1 | 1      |  |  |  |  |

equivalence 0 coincidence X-NOR

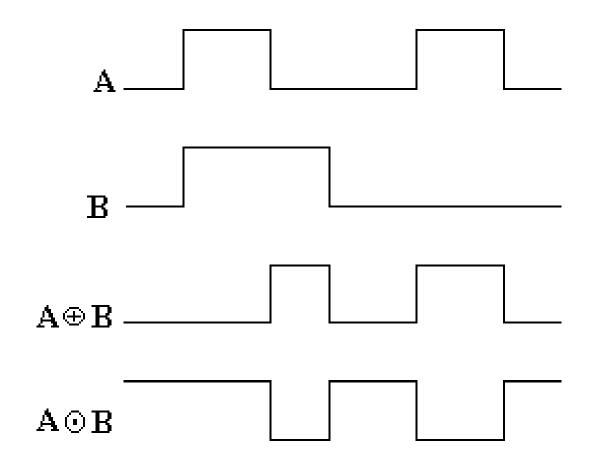

## Timing diagram

#### **INTEGRATED CIRCUIT LOGIC FAMILIES**

- Diode Logic (DL)

- Resistor-Transistor Logic (RTL)

- Diode-Transistor Logic (DTL)

- Transistor-Transistor Logic (TTL)

- Emitter-Coupled Logic (ECL)

- **CMOS Logic**

#### Fan-in

The number of standard loads drawn by an input to ensure reliable operation. Most inputs have a fan-in of 1.

#### Fan-out

The number of standard loads that can be reliably driven by an output, without causing the output voltage to shift out of its legal range of values.

# Comparison of performance characteristics of CMOS, TTL and ECL logic gates.

| Technolog   | СМО     | СМО    | TT  | TTL | TT   | TTL  | TTL | ECL  |

|-------------|---------|--------|-----|-----|------|------|-----|------|

| у           | S       | S      | L   | LS  | L    | ALS  | AS  |      |

|             | (silico | (metal | std |     | S    |      |     |      |

|             | n       | gate)  |     |     |      |      |     |      |

|             | gate)   |        |     |     |      |      |     |      |

| Device      | 74HC    | 4000   | 74  | 74L | 74S  | 74AL | 74A | 10K  |

| series      |         | В      |     | S   |      | S    | S   | Η    |

| Power       |         |        |     |     |      |      |     |      |

| dissipation |         |        |     |     |      |      |     |      |

| :           |         | 1 uW   | 10  | 2   | 19   | 1 mW | 8.5 | 25   |

| Static      |         |        | m   | mW  | m    |      | mW  | mW   |

|             |         |        | W   |     | W    |      |     |      |

| At 100      | 0.17    | 0.1    | 10  | 2   | 19   | 1 mW | 8.5 | 25   |

| kHz         | mW      | mW     | m   | mW  | m    |      | mW  | mW   |

|             |         |        | W   |     | W    |      |     |      |

| Propagatio  | 8 ns    | 50 ns  | 10  | 10  | 3 ns | 4 ns | 1.5 | 1 ns |

| n delay     |         |        | ns  | ns  |      |      | ns  |      |

| time        |         |        |     |     |      |      |     |      |

| Fan-out     |         |        | 10  | 20  | 20   | 20   | 40  |      |

Std : standard

LS: Low power Schottky S:

S: Schottky

# IEEE symbols for logic gates